| |

ChristopherJam

Registered: Aug 2004

Posts: 1427 |

Unexpected linecrunch

I'm sure in the past I've displayed full screen FLI just by writing a new value to $d011 every 23 cycles, and using some of the intervening time to update $d018 (ie, writing to $d011 on what vic artikel refers to as cycle 14).

However, if I have sprites zero to five enabled, and am only writing d011 every second line, it appears that I need to perform the first $d011 write for new char rows at least one cycle earlier, lest I get a linecrunch.

Any idea what's going on here?

(every two lines, I'm running something like this:

lda#efy0+ 71:sta $d007

lda#d18v0

ldx#$38+1

ldy#0

sta $d018

sty VM0+$3f8:iny

sty VM0+$3f9:iny

sty VM0+$3fa:iny

sty VM0+$3fb:iny

sty VM0+$3fc:iny

sty VM0+$3fd:nop

stx $d011

Also: not sure if it's relevant, but I stabilise the interrupt by forcing a DMA one and a half lines before the first such block of code is run, ie the first block is preceded by

sta $d011 ; trigger badline just before effct starts; this one's just to stabilise

nop:nop:nop:nop:nop:nop ;extra nops because there's no sprite DMA at the end of the above DMA

|

|

| |

Oswald

Registered: Apr 2002

Posts: 5129 |

sprite 0-3 is fetched in left side IIRC, so they interfere with your timing I guess.

+

BA goes low three cycles before the VIC access. After that,

AEC remains low during the second phase and the VIC performs the

accesses. Why three cycles? BA is connected to the RDY line of the

processor as mentioned, but this line is ignored on write accesses

(the CPU can only be interrupted on reads), and the 6510 never does

more than three writes in sequence (see [5]). |

| |

ChristopherJam

Registered: Aug 2004

Posts: 1427 |

Nah, right side, though six sprites doesn't leave much time before the visible area.

victimer gives the following:

[Onyx:~/c64/victimer/victimer] ./victimer -s 63

| 1 1 1 1 1 1 1 1 1 1 2 2 2 2 2 2 2 2 2 2 3 3 3 3 3 3 3 3 3 3 4 4 4 4 4 4 4 4 4 4 5 5 5 5 5 5 5 5 5 5 6 6 6 6 |

0 |1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 |

| |===========01020304050607080910111213141516171819202122232425262728293031323334 353637383940===========| |

--|----------------------------------------------------------------------------- -------------------------------------------------|

| x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x x W W w |

| r r r r r g g g g g g g g g g g g g g g g g g g g g g g g g g g g g g g g g g g g g g g g |

ss|3sss4sss5sss6 7 0sss1sss2sss|

| i i i i |

--|----------------------------------------------------------------------------- -------------------------------------------------|

| ^(close sideborder) ^(open sideborder)

| ^---FLI-----------------> ^-----^(double line)

| ^---DMA Delay--------------------------------------------------------------^

sprenable=3f

CPU: 48 (+ 2=50)

VIC: 12 (+ 1=13)

63

x - CPU regular cycles

W - CPU write cycles

w - CPU 3rd write cycle

c - VIC video ram

g - VIC color ram

0..7 - VIC sprite pointer fetches

s - VIC sprite data accesses

i - VIC idle accesses

I should probably see if I can duplicate the effect with sprites disabled mind.

Main thing that's confusing me is I thought linecrunch came from cancelling a DMA, not triggering a new one.. |

| |

JackAsser

Registered: Jun 2002

Posts: 2038 |

You can't "cancel" a DMA. If it started the CPU is locked until the DMA is completed. If you postpone a DMA you effectively get FLD. If you induce a DMA you get, depending on timing, line crunch or VSP. Right? |

| |

lft

Registered: Jul 2007

Posts: 369 |

Actually, I concur with ChristopherJam on the terminology: Linecrunch cancels DMA (before it starts).

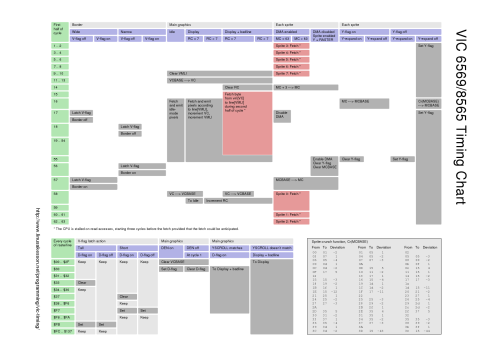

When you FLI on line 7 of a char row, VIC will be in badline state during cycle 58 (as numbered according to the VIC article). This causes RC to wrap to 0, and VIC remains in display state.

But when you FLI on every other line, line 7 will be a normal display line. During cycle 58, VIC will be in display state (not badline state). This causes VIC to enter the idle state and RC to remain at 7.

Then, if you try to FLI on the following line, you will actually trigger a VSP with offset 0. This looks like a linecrunch (VC is incremented by 40), except for some side effects (DMA, after which RC is incremented to zero). Move the "FLI" one cycle earlier, and you instead set up a regular badline, where RC is cleared on cycle 14.

Get the PDF

Hope this helps! |

| |

Count Zero

Registered: Jan 2003

Posts: 2026 |

Idiot crackers such as me are never helped enough. Lovely thread! (gotta print the PDF in large and pin it near the mirror over my bed (next to the face of lft :) ) !!1!) |

| |

ChristopherJam

Registered: Aug 2004

Posts: 1427 |

Quoting lftBut when you FLI on every other line, line 7 will be a normal display line. During cycle 58, VIC will be in display state (not badline state). This causes VIC to enter the idle state and RC to remain at 7.

Then, if you try to FLI on the following line, you will actually trigger a VSP with offset 0. This looks like a linecrunch (VC is incremented by 40), except for some side effects (DMA, after which RC is incremented to zero)

Ah! OK, that makes sense. TBH I should have known something was up when I needed to perform the very first DMA for the effect area one cycle earlier too; the situation is the same.

This is my first every-second-line effect and it's kind of showing. I need to study that diagram some more.

Thanks for the help :) |

| |

Oswald

Registered: Apr 2002

Posts: 5129 |

so while the cycle counters are watching I'd like to hijack the thread :)

is it possible to repeat full char rows endlessly with one d011 write per 8 rasterlines ? about what cycle which row inside char, and what to write to d011 ? :) |

| |

JackAsser

Registered: Jun 2002

Posts: 2038 |

Quote: so while the cycle counters are watching I'd like to hijack the thread :)

is it possible to repeat full char rows endlessly with one d011 write per 8 rasterlines ? about what cycle which row inside char, and what to write to d011 ? :)

Yes, I did that in the chess roto zoomer in Andropolis. Or rather every 7th actually, but I suppose every 8th works as well? |

| |

Radiant

Registered: Sep 2004

Posts: 640 |

I think it has to be every seventh. The way you do it is by triggering a badline during cycles 54-57 (IIRC) when RC=7. |

| |

Radiant

Registered: Sep 2004

Posts: 640 |

I did it just now in "The Social Demo". :-) |

... 57 posts hidden. Click here to view all posts....

|

| Previous - 1 | 2 | 3 | 4 | 5 | 6 | 7 - Next |